# Technical Information Manual

Revision n. 6 6 December 2005

V1190 A/B

VX1190 A/B

MULTIHIT TDCs

MANUAL REV.6

NPO: 00104/03:V1X90.MUTx/06

CAEN will repair or replace any product within the guarantee period if the Guarantor declares that the product is defective due to workmanship or materials and has not been caused by mishandling, negligence on behalf of the User, accident or any abnormal conditions or operations.

CAEN declines all responsibility for damages or injuries caused by an improper use of the Modules due to negligence on behalf of the User. It is strongly recommended to read thoroughly the CAEN User's Manual before any kind of operation.

CAEN reserves the right to change partially or entirely the contents of this Manual at any time and without giving any notice.

# TABLE OF CONTENTS

| 1. G          | ENERAL DESCRIPTION                  | 10 |

|---------------|-------------------------------------|----|

| 1.1.          | Overview                            | 10 |

| 1.2.          | BLOCK DIAGRAM                       | 11 |

| 2. FU         | UNCTIONAL DESCRIPTION               | 12 |

| 2.1.          | HPTDC overview                      |    |

|               | 1.1. TDC chips architecture         |    |

| 2.2.          | OPERATING MODE SELECTION            |    |

| 2.3.          | CONTINUOUS STORAGE MODE             |    |

| 2.4.<br>2.4   | Trigger Matching Mode               |    |

| 2.5.          | INTEGRAL-NON-LINEARITY COMPENSATION | 18 |

| 3. TI         | ECHNICAL SPECIFICATIONS             | 22 |

| 3.1.          | PACKAGING                           | 22 |

| 3.2.          | Power requirements                  | 22 |

| 3.3.          | Front Panel                         | 23 |

| 3.4.          | External connectors                 |    |

|               | 4.1. INPUT connectors               |    |

|               | 4.3. EXTERNAL TRIGGER connectors    |    |

| 3.5.<br>3.5   | OTHER FRONT PANEL COMPONENTS        |    |

| 3.6.          | Internal hardware components        | 27 |

| 3.6           | 6.1. Switches                       | 27 |

| 3.7.          | TECHNICAL SPECIFICATIONS TABLE      | 29 |

| <b>4. O</b> ] | PERATING MODES                      | 30 |

| 4.1.          | Installation                        | 30 |

| 4.2.          | Power ON sequence                   | 30 |

| 4.3.          | Power ON STATUS                     | 31 |

| 4.4.          | ADDRESSING CAPABILITY               |    |

|               | 4.1. Addressing via Base Address    |    |

|               | 4.2. Base addressing examples       |    |

|               | 4.4. MCST/CBLT addressing examples  |    |

| 4.5.          | Interrupter capability              |    |

|               | 5.1. Interrupt Status/ID            |    |

|               | 5.2. Interrupt Level                |    |

|               | 5.3. Interrupt Generation           |    |

| 4.5           | 5.4. Interrupt Request Release      | 36 |

Title:

|    | 4.6. T           | RIGGER MATCHING MODE DATA TRANSFER                                               | 37       |

|----|------------------|----------------------------------------------------------------------------------|----------|

|    | 4.6.1.           | D32 OUTPUT BUFFER readout (Trigger Matching)                                     | 37       |

|    | 4.6.2.           | BLT32/64 OUTPUT BUFFER readout with Bus Error and Event Aligned BLT disabled     | 37       |

|    | 4.6.3.           | BLT32/64 OUTPUT BUFFER readout with Bus Error enabled                            |          |

|    | 4.6.4.           | BLT32/64 OUTPUT BUFFER readout with Event Aligned BLT enabled                    |          |

|    | 4.6.5.           | BLT32/64 OUTPUT BUFFER readout with both Event Aligned BLT and Bus Error enabled |          |

|    | 4.6.6.           | CBLT32/64 OUTPUT BUFFER readout                                                  |          |

|    | 4.6.7.           | D32 and BLT32/MBLT readout with Event FIFO enabled                               | 41       |

|    | 4.7. C           | OUNTINUOUS STORAGE MODE DATA TRANSFER                                            | 42       |

|    | 4.7.1.           | D32 OUTPUT BUFFER readout (Continuous Storage)                                   | 42       |

|    | 4.7.2.           | BLT32/64 OUTPUT BUFFER readout (Continuous Storage)                              | 43       |

|    | 4.8. R           | ESET LOGIC                                                                       | 43       |

|    | 4.8.1.           | Software and Hardware CLEAR                                                      |          |

|    | 4.8.2.           | Software RESET                                                                   |          |

|    | 4.8.3.           | Hardware RESET                                                                   |          |

|    | 4.8.4.           | Software Event Count RESET                                                       | 44       |

|    | 4.8.5.           | Hardware Bunch Count RESET                                                       | 44       |

|    | 4.9. F           | RMWARE UPGRADE                                                                   | 45       |

|    | T.J. 1           | INWARD OF GRADE.                                                                 |          |

| 5. | OPER             | ATING CODES                                                                      | 46       |

| •  | 0121             |                                                                                  |          |

|    | 5.1. P           | ROGRAMMING CAPABILITY                                                            | 46       |

|    | 5 2 A            | COLUCIATION MODE ON CODE                                                         | 40       |

|    | 5.2. A 5.2.1.    | CQUISITION MODE OPCODES                                                          | 49<br>40 |

|    | 5.2.1.<br>5.2.2. | Set Continuous Storage Mode (CODE 00xx)                                          | 49<br>10 |

|    | 5.2.3.           | Read acquisition mode (CODE 02xx)                                                |          |

|    | 5.2.4.           | Set keep_token (CODE 03xx)                                                       |          |

|    | 5.2.5.           | Clear keep_token (CODE 04xx)                                                     |          |

|    | 5.2.6.           | Load default configuration (CODE 05xx)                                           |          |

|    | 5.2.7.           | Save User configuration (CODE 06xx)                                              |          |

|    | 5.2.8.           | Load User configuration (CODE 07xx)                                              |          |

|    | 5.2.9.           | Set auto load User configuration (CODE 08xx)                                     |          |

|    | 5.2.10           | Set auto load default configuration (CODE 09xx)                                  | 50       |

|    | 5.3. T           | RIGGER OPCODES                                                                   | 51       |

|    | 5.3.1.           | Set window width (CODE 10xx)                                                     |          |

|    | 5.3.2.           | Set window offset (CODE 11xx)                                                    |          |

|    | 5.3.3.           | Set extra search margin (CODE 12xx)                                              | 51       |

|    | 5.3.4.           | Set reject margin (CODE 13xx)                                                    |          |

|    | 5.3.5.           | Enable subtraction of trigger time (CODE 14xx)                                   |          |

|    | 5.3.6.           | Disable subtraction of trigger time (CODE 15xx)                                  |          |

|    | 5.3.7.           | Read trigger configuration (CODE 16xx)                                           | 52       |

|    | 5.4. T           | DC EDGE DETECTION AND RESOLUTION OPCODES                                         | 52       |

|    | 5.4.1.           | Set edge detection configuration (CODE 22xx)                                     | 52       |

|    | 5.4.2.           | Read edge detection configuration (CODE 23xx)                                    |          |

|    | 5.4.3.           | Set LSB of leading/trailing edge (CODE 24xx)                                     |          |

|    | 5.4.4.           | Set leading time and width resolution when pair (CODE 25xx)                      |          |

|    | 5.4.5.           | Read resolution (CODE 26xx)                                                      |          |

|    | <i>5.4.6.</i>    | Set channel dead time between hits (CODE 28xx)                                   |          |

|    | 5.4.7.           | Read channel dead time between hits (CODE 29xx)                                  | 33       |

|    | 5.5. T           | DC READOUT OPCODES                                                               |          |

|    | 5.5.1.           | Enable TDC Header and Trailer in readout (CODE 30xx)                             |          |

|    | 5.5.2.           | Disable TDC Header and Trailer in readout (CODE 31xx)                            | 5.5      |

| <i>5.5.3</i> . | Read TDC Header and Trailer status (CODE 32xx)     |    |

|----------------|----------------------------------------------------|----|

| <i>5.5.4</i> . | Set maximum number of hits per event (CODE 33xx)   |    |

| 5.5.5.         | Read maximum number of hits per event (CODE 34xx)  |    |

| 5.5.6.         | Enable TDC error mark (CODE 35xx)                  |    |

| <i>5.5.7</i> . | Disable TDC error mark (CODE 36xx)                 |    |

| 5.5.8.         | Enable bypass TDC if error (CODE 37xx)             |    |

| 5.5.9.         | Disable bypass TDC if error (CODE 38xx)            |    |

| 5.5.10.        |                                                    |    |

| 5.5.11.        | Read enabled TDC internal error type (CODE 3Axx)   | 57 |

| 5.5.12.        | z = -i $z = -i $ $z = -i$                          |    |

| 5.5.13.        | Read effective size of readout FIFO (CODE3Cxx)     | 58 |

| 5.6. C         | HANNEL ENABLE OPCODES                              | 58 |

| 5.6.1.         | Enable channel nn (CODE 40nn)                      | 58 |

| 5.6.2.         | Disable channel nn (CODE 41nn)                     | 58 |

| 5.6.3.         | Enable all channels (CODE 42xx)                    | 59 |

| 5.6.4.         | Disable all channels (CODE 43xx)                   | 59 |

| 5.6.5.         | Write enable pattern (CODE 44xx)                   | 59 |

| 5.6.6.         | Read enable pattern (CODE 45xx)                    | 59 |

| 5.6.7.         | Write enable pattern 32 (CODE 460n)                | 60 |

| 5.6.8.         | Read enable pattern 32 (CODE 470n)                 | 60 |

| 5.7. A         | DJUST OPCODES                                      | 61 |

| 5.7.1.         | Set global offset (CODE 50xx)                      | 61 |

| 5.7.2.         | Read global offset (CODE 51xx)                     | 61 |

| 5.7.3.         | Set channel nn adjust (CODE 52nn)                  |    |

| 5.7.4.         | Read channel nn adjust (CODE 53nn)                 | 61 |

| 5.7.5.         | Set RC adjust of TDC n (CODE 540n)                 | 61 |

| 5.7.6.         | Read RC adjust of TDC n (CODE 550n)                |    |

| 5.7.7.         | Save RC adjust on EEPROM (CODE 56xx)               | 62 |

| 5.8. M         | ISCELLANEOUS                                       | 62 |

| 5.8.1.         | Read ID code of TDC n (CODE 600n)                  |    |

| 5.8.2.         | Read firmaware rev. of microcontroller (CODE 61xx) |    |

| 5.8.3.         | Reset PLL and DLL (CODE 62xx)                      | 62 |

| 5.9. A         | DVANCED                                            | 62 |

| 5.9.1.         | Write word nn into the Scan Path Setup (CODE 70nn) |    |

| 5.9.2.         | Read word nn into the Scan Path Setup (CODE 71nn)  |    |

| 5.9.3.         | Load the Scan Path Setup (CODE 72xx)               | 63 |

| 5.9.4.         | Reload the default Scan Path Setup (CODE 73xx)     |    |

| 5.9.5.         | Read errors in the TDC n status (CODE 740n)        |    |

| 5.9.6.         | Read the DLL LOCK bit of the TDC n (CODE 750n)     |    |

| 5.9.7.         | Read the TDC n status (CODE 760n)                  |    |

| 5.9.8.         | Load the Scan Path Setup in the TDC n (CODE 770n)  |    |

| 5.10.          | TEST AND DEBUG                                     | 64 |

| 5.10.1.        |                                                    |    |

| 5.10.2.        |                                                    |    |

| 5.10.3.        |                                                    |    |

| 5.10.4.        | · · · · · · · · · · · · · · · · · · ·              |    |

| 5.10.5.        |                                                    |    |

| 5.10.6.        |                                                    |    |

| 5.10.7.        |                                                    |    |

| 5.10.8.        |                                                    |    |

| 5.10.9.        |                                                    |    |

| 5.10.10        |                                                    |    |

|                |                                                    |    |

| VME 1          | INTERFACE                                          | 67 |

| 6.1.<br><i>6.1</i> | REGISTER ADDRESS MAP                       |    |

|--------------------|--------------------------------------------|----|

| 6.2.               |                                            |    |

|                    | 2.1. Trigger Matching Mode                 | 69 |

|                    | 2.2. Continuous Storage Mode               |    |

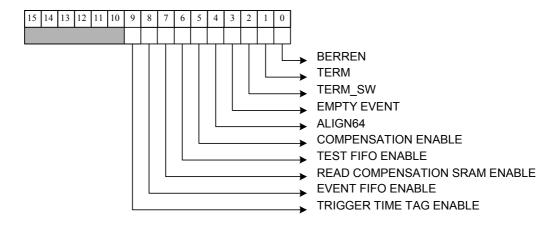

| 6.3.               | Control Register                           |    |

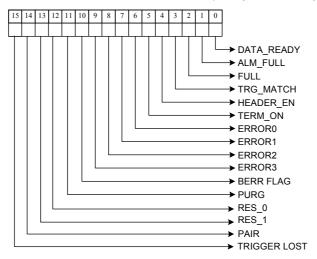

| 6.4.               | Status Register                            |    |

| 6.5.               | ADER 32 REGISTER (ONLY FOR VX1190 A/B)     | 75 |

| 6.6.               | ADER 24 REGISTER (ONLY FOR VX1190 A/B)     | 75 |

| 6.7.               | Enable Ader Register (only for VX1190 A/B) | 76 |

| 6.8.               | Interrupt Level Register                   | 76 |

| 6.9.               | Interrupt Vector Register                  | 76 |

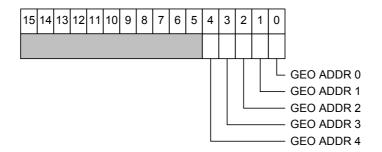

| 6.10.              | GEO Address Register                       | 77 |

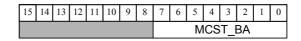

| 6.11.              | MCST Base Address Register                 | 77 |

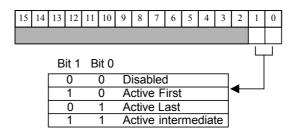

| 6.12.              | MCST/CBLT CONTROL REGISTER                 | 78 |

| 6.13.              | Module Reset Register                      | 78 |

| 6.14.              | Software Clear Register                    | 78 |

| 6.15.              | SOFTWARE EVENT RESET REGISTER              | 78 |

| 6.16.              | Software Trigger Register                  | 78 |

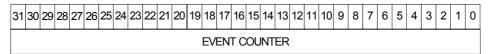

| 6.17.              | Event Counter Register                     | 79 |

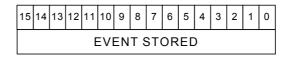

| 6.18.              | Event Stored register                      | 79 |

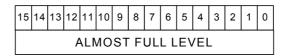

| 6.19.              | Almost Full Level Register                 | 79 |

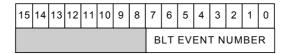

| 6.20.              | BLT Event Number Register                  | 80 |

| 6.21.              | FIRMWARE REVISION REGISTER                 | 80 |

| 6.22.              | Testreg Register                           | 80 |

| 6.23.              | OUT_PROG CONTROL REGISTER                  | 81 |

| 6.24.              | Micro Register                             | 81 |

| 6.25.              | MICRO HANDSHAKE REGISTER                   | 81 |

| 6.26.              | DUMMY32 REGISTER                           | 82 |

| 6.27.              | DUMMY16 REGISTER                           | 82 |

| 6.28.              | SELECT FLASH REGISTER                      | 82 |

| 6.29.              | FLASH MEMORY                               | 82 |

| 6.30.              | COMPENSATION SRAM PAGE REGISTER            | 82 |

| 6.31.              | EVENT FIFO                                 | 83 |

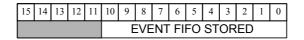

| 6.32.              | EVENT FIFO STORED REGISTER                 | 83 |

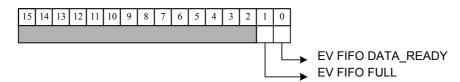

| 6.33.              | EVENT FIFO STATUS REGISTER                 | 83 |

COMPENSATION SRAM ......84

6.34.

| APPENDIX A: FLASH MEMORY ACCESSES                                                   | 85 |

|-------------------------------------------------------------------------------------|----|

| APPENDIX B: DEFAULT SET UP SCAN PATH                                                | 90 |

| REFERENCES                                                                          | 94 |

| LIST OF FIGURES                                                                     |    |

| Fig. 1.1: Mod. V1190 A Block Diagram                                                | 11 |

| FIG. 2.1: TDC SIMPLIFIED BLOCK DIAGRAM                                              | 12 |

| Fig. 2.2: Pulse detection                                                           | 13 |

| Fig. 2.3: Continuous storage                                                        | 15 |

| Fig. 2.4: Mod. V1190 A/B Trigger Matching Mode timing diagram                       | 16 |

| Fig. 2.5: Trigger matching windows overlap                                          | 17 |

| FIG. 2.6: STORAGE OF HITS OCCURRED PRIOR TRIGGERING                                 | 17 |

| FIG. 2.7: STORAGE OF HITS WHICH MAY OCCUR AFTER TRIGGERING                          | 18 |

| Fig. 2.8 INL I/O Characteristic                                                     | 19 |

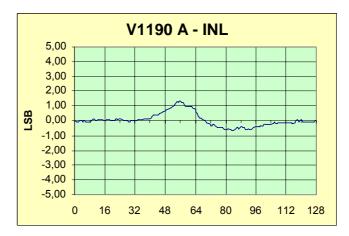

| Fig. 2.9 INL trace @ 200ps                                                          | 19 |

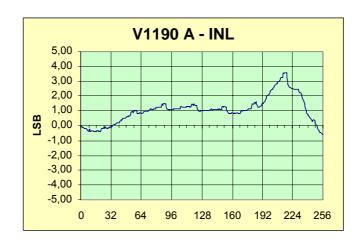

| Fig. 2.10 INL trace @ 100ps                                                         | 20 |

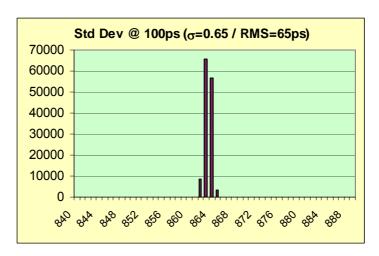

| Fig. 2.11 RMS example @ 100ps (T4=85ns) after INL compensation                      | 20 |

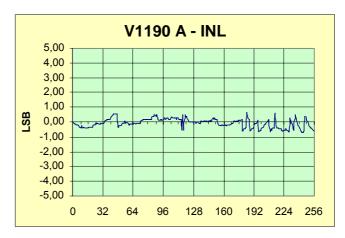

| FIG. 2.12 INL FOR 100 PS AFTER INL COMPENSATION                                     | 21 |

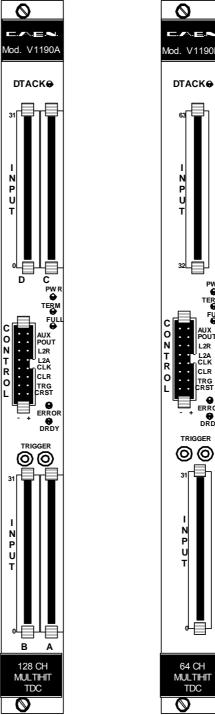

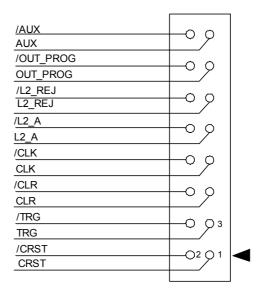

| Fig. 3.1: Model V1190 A/V1190 B front panels                                        | 23 |

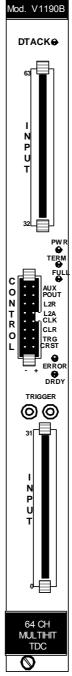

| FIG. 3.2: INPUT CONNECTOR PIN ASSIGNMENT                                            | 24 |

| FIG. 3.3: INPUT CONNECTOR CABLING (MOD. A967 CABLE ADAPTER)                         | 25 |

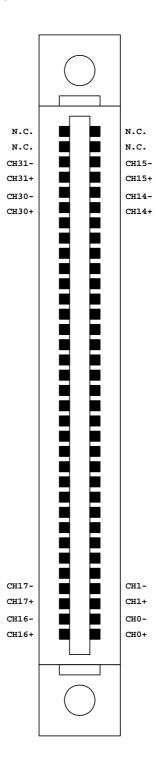

| FIG. 3.4: CONTROL CONNECTOR PIN ASSIGNMENT                                          | 26 |

| FIG. 3.5: COMPONENT LOCATION (V1190 A)                                              | 28 |

| Fig. 4.1: Base Addressing: Example 1                                                | 33 |

| FIG. 4.2: MCST/CBLT Addressing Example                                              | 35 |

| FIG. 4.3 EXAMPLE OF BLT DATA TRANSFER WITH BERR AND EVENT ALIGNED BLT DISABLED      | 38 |

| FIG. 4.4 EXAMPLE OF BLT DATA CYCLE WITH BERR ENABLED AND EVENT ALIGNED BLT DISABLED | 38 |

| FIG. 4.5 EXAMPLE OF BLT DATA CYCLE WITH BERR DISABLED AND EVENT ALIGNED BLT ENABLED | 39 |

| FIG. 4.6 EXAMPLE OF BLT DATA TRANSFER WITH BERR AND EVENT ALIGNED BLT ENABLED       | 40 |

| Fig. 4.7 MEB readout with Event FIFO enabled                                        | 42 |

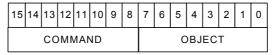

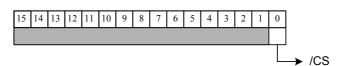

| Fig. 5.1: Micro Register                                                            | 46 |

| Fig. 5.2: Output Buffer: the Test word                                              | 65 |

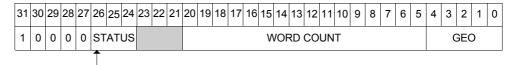

| Fig. 6.1: Output Buffer: the Global Header                                          | 69 |

| Fig. 6.2: Output Buffer: the TDC Header                                             | 69 |

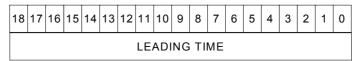

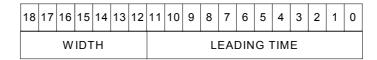

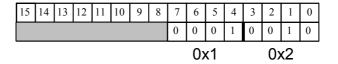

| FIG. 6.3: OUTPUT BUFFER; THE TDC MEASUREMENT                                        | 70 |

| FIG. 6.4: OUTPUT BUFFER: THE TDC TRAILER            | 70 |

|-----------------------------------------------------|----|

| FIG. 6.5: OUTPUT BUFFER: THE TDC ERROR              | 70 |

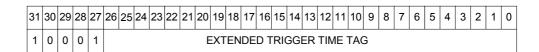

| FIG. 6.6: OUTPUT BUFFER: THE TRIGGER TIME TAG.      | 70 |

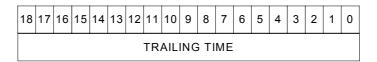

| FIG. 6.7: OUTPUT BUFFER: THE TRAILER                | 70 |

| FIG. 6.8: OUTPUT BUFFER: THE FILLER                 | 71 |

| Fig. 6.9: Control Register                          | 72 |

| Fig. 6.10: Status Register                          | 74 |

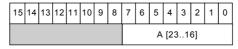

| Fig. 6.11: ADER 32 Register                         | 75 |

| Fig. 6.12: ADER 24 Register                         | 75 |

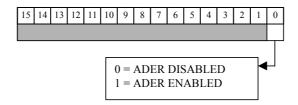

| Fig. 6.13: Enable ADER Register                     | 76 |

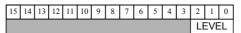

| Fig. 6.14: Interrupt Level Register                 | 76 |

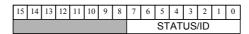

| Fig. 6.15: Interrupt Vector Register                | 76 |

| Fig. 6.16: Geographical address register            | 77 |

| Fig. 6.17: MCST/CBLT address register               | 77 |

| Fig. 6.18: MCST/CBLT Control Register               | 78 |

| Fig. 6.19: Trigger Counter Register                 | 79 |

| Fig. 6.20: Event Stored Register                    | 79 |

| Fig. 6.21: Almost Full Level Register               | 79 |

| Fig. 6.22: BLT Event Number Register                | 80 |

| Fig. 6.23 Firmware Revision Register                | 80 |

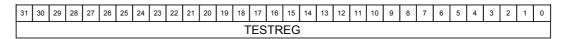

| Fig. 6.24: Testreg Register                         | 80 |

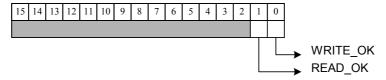

| Fig. 6.25: Out_Prog Register.                       | 81 |

| Fig. 6.26: Micro Register                           | 81 |

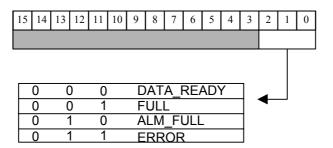

| Fig. 6.27: Micro Handshake register                 | 81 |

| Fig. 6.28: Select Flash register                    | 82 |

| Fig. 6.29: Compensation Sram Page register          | 83 |

| Fig. 6.30: Event FIFO register                      | 83 |

| Fig. 6.31: Event FIFO Stored register               | 83 |

| Fig. 6.32: Event FIFO Status register               | 83 |

| FIG. 6.33: COMPENSATION SRAM ARCHITECTURE           | 84 |

| FIG. A.1: FLASH ARCHITECTURE                        | 85 |

| LIST OF TABLES                                      |    |

| TABLE 3.1: MODEL V1190 A/B POWER REQUIREMENTS       | 22 |

| Table 3.2: Model V1190 A/B technical specifications | 29 |

| TABLE 4.1: MODULE RECOGNISED ADDRESS MODIFIER       | 32 |

|                                                     |    |

### Title: Mod. V1190-VX1190 A/B, 128/64 Ch Multihit TDC

**Revision date:** 06/12/2005

**Revision:** 6

| TABLE 4.2: CLEAR/RESET EFFECT ON THE MODEL V1190 A/B REGISTERS | 45 |

|----------------------------------------------------------------|----|

| TABLE 5.1: OPERATING CODES LIST                                | 47 |

| TABLE 6.1: ADDRESS MAP FOR THE MODEL V1190 A/B                 | 67 |

| TABLE 6.2: ROM ADDRESS MAP FOR THE MODEL V1190 A/B             | 68 |

| TADLE D. 7. DEFAULT SET UD SCAN DATU                           | 00 |

# 1. General description

## 1.1. Overview

The Model V1190 A is a 1-unit wide VME 6U module that houses 128 independent Multi-Hit/Multi-Event Time to Digital Conversion channels. The unit houses 4 High Performance TDC chips, developed by CERN/ECP-MIC Division. Resolution can be set at 100 ps (19 bit dynamics,  $52 \mu s$  FSR), 200 ps (19 bit dynamics,  $104 \mu s$  FSR) or 800 ps (17 bit dynamics,  $104 \mu s$  FSR).

The Model V1190 B is a 1-unit wide VME 6U module that houses 64 independent Multi-Hit/Multi-Event Time to Digital Conversion channels. The unit houses 2 High Performance TDC chips and shares most of its features with the V1190 A.

The VX1190 A and the VX1190 B are the VME64X mechanics versions of the Mod. V1190 A and of the Mod. V1190 B respectively. They provide all the features of the std. VME versions, moreover they support the GEOgraphical Address.

The CERN/ECP-MIC HPTDC is a General Purpose time-to-digital converter, with 32 channels per chip. The chips can be enabled to the detection of the rising and/or falling edges and of the pulses width.

The data acquisition can be programmed in "EVENTS" ("TRIGGER MATCHING MODE" with a programmable time window: the so called *match window*) or in "CONTINUOUS STORAGE MODE".

The board houses a 32 kwords deep Output Buffer, that can be readout via VME (as single data, Block Transfer and Chained Block Transfer) in a completely independent way from the acquisition itself.

The TDCs' programming is performed via a microcontroller that implements a high-level interface towards the User in order to mask the TDCs' hardware.

Both the Mod. V1190 A and the Mod. V1190 B fit into standard, V430 and VME64x VMEbus crates.

The Mod. VX1190 A and the Mod. VX1190 B require VME64x VMEbus crates.

The module accepts both ECL and LVDS inputs on the TDC inputs.

The unit accepts the following CONTROL signals (ECL differential, 110  $\Omega$ ) in common to all channels:

TRG: a common TRIGGER input;

CRST: allows the TDCs' Bunch Count Reset (see § 4.8.5)<sup>1</sup>;

CLK: allows to provide an external Clock to the board;

CLR: erases data from the Output Buffer and performs TDCs global reset;

L2A/L2R: Level 2 Accept/Reject (2<sup>nd</sup> level trigger, not yet implemented);

AUX: auxiliary input (not yet implemented).

The TRIGGER can be also sent as NIM signal on a double (bridged) LEMO00 connector.

-

<sup>&</sup>lt;sup>1</sup> Refer also to [4] **J. Christiansen, "HPTDC Version 2.0"**, for details

An ECL output, OUT\_PROG, whose function can be programmed (see § 6.23), is also available on the CONTROL Bus.

Six front panel LEDs show the status of the unit:

- DTACK lights up each time the module generates the VME signal DTACK;

- PWR lights up when the module is correctly supplied

- TERM ON lights up when all the lines of the CONTROL bus are terminated;

- FULL lights up when the memory is full;

- ERROR lights up when a global error in the TDCs occurs;

- DATA READY lights up when the Event/Data Ready condition occurs (see § 6.4).

The module houses a VME INTERRUPTER [2]: the interrupt is generated as soon as the buffer is almost full (programmable).

The module works in A24/A32 mode.

The internal registers are available in D16 / D32 mode, while the data buffer is available in D32, BLT32 or MBLT64. The module supports also the Chained Block Transfer mechanism (CBLT) and the Multicast commands (MCST), see § 4 for the module's addressing and data transfer details.

N.B.: in the present manual the "generic" term "V1190" refers to all versions; "V1190 A" refers to both V1190 A and VX1190 A; "V1190 B" refers to both V1190 B and VX1190 B; except as otherwise specified.

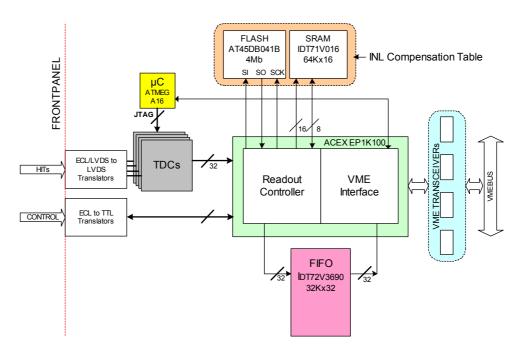

# 1.2. Block Diagram

Fig. 1.1: Mod. V1190 A Block Diagram

The function of each block will be explained in detail in the following sections.

**NPO:** 00104/03:V1X90.MUTx/06

**Filename:** V1190\_REV6.DOC

Number of pages:

# 2. Functional description

## 2.1. HPTDC overview

The modules are based on High Performance TDC chips, developed by CERN/ECP-MIC Division [4].

In order to achieve a better use of the module, an overview of the TDC chips operation will be shown in the following sections.

## 2.1.1. TDC chips architecture

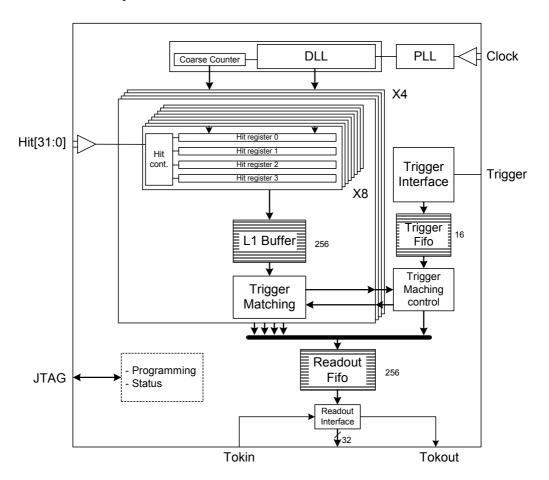

Fig. 2.1: TDC Simplified Block Diagram

The time base for the TDC measurements is a Delay Locked Loop (DLL) with 32 delay elements and a clock synchronous counter (coarse counter), both driven from the same clock reference. The clock reference can be taken directly from the clock input of the TDC chip (40 MHz) or can come from an on-chip PLL; the PLL can be used as a filter to

**NPO:** 00104/03:V1X90.MUTx/06

Filename: V1190\_REV6.DOC Number of pages:

6

remove jitter on the input clock (40 MHz) or can perform clock multiplication (160/320 MHz) to increase time resolution:

40 MHz (clock input or clock filtered) and DLL with 32 delay elements → 781 ps (800 ps) 160 MHz and DLL with 32 delay elements  $\rightarrow$  195 ps (200 ps) 320 MHz and DLL with 32 delay elements  $\rightarrow$  98 ps (100 ps)

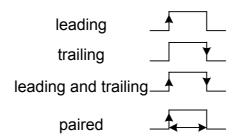

A hit measurement is performed by storing the state of the DLL (fine/vernier counter) and the coarse counter in one hit register when a hit is detected. The TDC can be programmed to detect individual leading and/or trailing edges of the hit signal, or alternatively to perform a paired measurement consisting of one leading edge and the corresponding pulse width.

Fig. 2.2: Pulse detection

Each channel can store 4 hit measurements before being written into a 256 words deep buffer (L1 buffer) shared by a group of 8 channels.

The hit registers content is written into the L1 buffer together with a channel identifier. A 8 bit channel dependant offset programmable is added to the measurement before writing it into the L1 buffer.

If the channel buffer is full, when a new hit arrives, it will be ignored.

The two operation modes will be described in detail in the relevant sections; at this point we must remember that, when the module works in Continuous Storage mode (see § 2.3), measurements stored in the L1 buffer are passed directly to a common Readout FIFO.

When the module works in Trigger Matching mode (see § 2.4) a trigger matching function selects hits related to a trigger. The trigger information, consisting of a trigger time tag (bunch id) and an event id, are stored temporarily in a 16 words deep Trigger FIFO. A time window of programmable size is available for the trigger matching to accommodate the time spread of hits related to the same event.

The read-out FIFO is 256 words deep and its main function is to enable data to be read out while others are being processed. The effective size of the readout FIFO can be "artificially" reduced via the programming.

The TDCs feature several readout interfaces (parallel, serial, via Jtag, byte wise).

The V1190 features a parallel readout with the FPGA like read-out controller and all TDCs in the chain configured as slaves. The master sends the token (Tokin in Fig. 2.1) to the first slave chip in the chain which then starts to send its data. The read-out of individual words are controlled by a Data ready / Get data handshake. The token (Tokout in Fig. 2.1) is then passed on to the following slave TDCs in the chain until it finally arrives at the master.

In continuous storage a slave TDC can be programmed to keep token until no more data; otherwise the TDC passes the token; in trigger matching mode each slave must be programmed in order to keep the token until the end of the event.

It is possible to configure the programmable features in the TDC via JTAG, and also to get access to test facilities built into the TDC.

Programming of the device is separated into two scan path groups: setup scan path and control scan path.

The JTAG setup scan path is used to load programming data that can not be changed while the TDC is actively running. The JTAG setup scan path consists of a 646 bit configuration sequence plus one parity bit; refer to [4], page 32 for a detailed description.

The JTAG control scan path is used to enable/disable channels which can be done while the TDC is actively running. The JTAG control scan path is also used to initialize the PLL and DLL after power up: it consists of a 38 bit configuration sequence plus one parity bit; refer to [4], page 39 for a detailed description.

The setup/control scan paths have a parity bit which is continuously monitored for potential parity errors caused by single event upsets. Any detected parity error will set the respective error bit in the JTAG status register. Via JTAG it is possible to get access to the status of the TDC at any time. to monitor the TDC error status and all internal buffers occupancies (refer to [4], page 40).

On V1190 TDC programming and status monitoring is performed by an on board microcontroller (see § 5).

The HPTDC features 3 types of reset (refer to [4], page 16):

Event count reset: loads the programmed event count offset into the event id counter (useful in Trigger Matching mode only);

Bunch count reset: loads the programmed offsets into the coarse time counter, the trigger time tag (bunch id) counter and the reject counter; pratically, it represents the T0 time reference.

Global reset: clears all buffers in the TDC, initialises all internal state machines and counters to their initial state and clears all detected error conditions.

See § 4.8 for details about the V1190 A/B reset logic.

### 2.2. Operating mode selection

Two different module setups are selectable via software for different acquisition scenarios, namely:

- Continuous Storage Mode

- **Trigger Matching Mode**

It is possible to switch from one operation setup to the other by simply reprogramming: the operating mode can be selected via the 00xx and 01xx OPCODES (see § 5.2).

N.B: with this operation the data in memory will be lost.

See § 6.2 for a full description of the data format.

### 2.3. **Continuous Storage Mode**

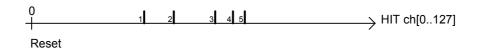

In this readout mode the data loaded into the L1 Buffer are straightly forwarded into the Readout FIFO of the TDC, where they are readout (by the FPGA master) and then loaded in the Output Buffer. All the hits received by the enabled channels are stored as valid data into the Output Buffer. The Time Origin (Time Zero) is represented by the latest RESET (see § 3.4.2).

Fig. 2.3: Continuous storage

The storage of data in the Output Buffer never foresees the writing of the control words (HEADER and TRAILER). The data are written in sequential order<sup>2</sup>, reflecting the time evolution of the external signals:

DATUM #1HIT time(1) DATUM #2HIT time(2) DATUM #3HIT time(3) DATUM #4HIT time(4) DATUM #5HIT time(5) DATUM #6HIT time(6)

If the total rate of HIT signals is higher than the transfer rate of the data from the TDCs to the Output Buffer (or from the Output Buffer to the VME) an overflow condition will be met:

### **OVERFLOW:**

Error word written into the FIFO Status register FULL bit set Trailer FULL bit = 1 into the Trailer

In this case there will be a data loss.

# 2.4. Trigger Matching Mode

Trigger matching is performed as a time match between a trigger time tag and the channel time measurements themselves. The trigger time tag is taken from the trigger FIFO and the time measurements are taken from the L1 buffer. Hits matching a trigger are passed to the common TDC readout FIFO.

A match between a trigger and a hit is detected within a programmable time window. The trigger matching control on the V1190 is handled through 4 programmable parameters<sup>3</sup> (see § 5.3.1 and § 5.3.4):

- match window,

- window offset,

- extra search margin,

- reject margin.

-

<sup>&</sup>lt;sup>2</sup> Hits closer than 100 ns might actually be misplaced.

<sup>&</sup>lt;sup>3</sup> The parameters programmable on the V1190 are functions of other 4 parameters which define the trigger matching function implemented in the HPTDC. The microcontroller translates the parameters set by the User on the V1190 into the parameters required by the chips.

Fig. 2.4: Mod. V1190 A/B Trigger Matching Mode timing diagram

The trigger is defined as the bunch ID when the event of interest occurred. The trigger matching being based on the bunch ID means that the "resolution" of the trigger matching is one clock cycle (25 ns) and the configuration parameters of the trigger matching mode are also specified in steps of clock cycles.

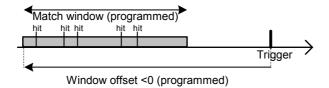

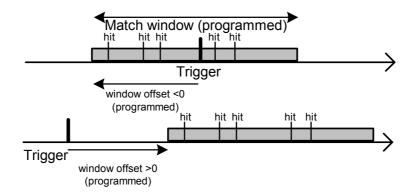

The window offset is the temporal distance (with sign, see Fig. 2.6 and Fig. 2.7) between the trigger and the start of the trigger matching window. A specific requirement of the trigger matching function implemented in the HPTDC is that the trigger must be subsequent to the match window. This is required to insure that all hits matching a trigger are already in the L1 buffer when a trigger matching search is started.

On the V1190 it is possible also to program a match window straddling the trigger or subsequently to the trigger (see  $\S$  2.4.1): in this case because an artificial delay (40 clock cycle = 1  $\mu$ s ) is induced on the trigger.

The search for hits matching a trigger is performed within an extended search window to guarantee that all matching hits are found even when the hits have not been written into the L1 buffer in strict temporal order. For normal applications it is sufficient to make the search window eight clock cycles larger than the match window (default setting for the V1190). The search window should be extended for applications where paired measurements of wide pulses are performed, as a paired measurement is not written into the L1 buffer before both leading and trailing edge have been digitized.

To prevent buffer overflows and to speed up the search time an automatic reject function reject older hits, when no triggers are waiting in the trigger FIFO. A separate reject counter runs with a programmable offset to detect hits to reject. The reject margin should be set to be at least 1 clock cycle to insure that no hits of interest are rejected.

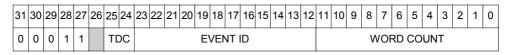

In trigger matching mode all data belonging to an event are written into the common read-out FIFO between a TDC Header and a TDC Trailer. The TDC Header contains an event id and a bunch id (trigger time tag) and the TDC Trailer contains the same event id plus the event word count.

The stored data can represent an absolute time measurement (where time 0 is the latest Bunch reset) or optionally all time measurements read out are referenced to the start of match window (see § 5.3.5 and 5.3.6).

The trigger matching can be programmed to match a defined maximum number of hits to each trigger. The hits assigned to an event is in this case done on a "first come first served" basis. If the limiting function has rejected hits this will be signalled via an error marking word in the end of the event.

In case an error condition (L1 buffer overflow, Trigger FIFO overflow, memory parity error, limiting number of hits matched to event, etc.) has been detected during the trigger matching a special word with error flags is generated.

A unique feature of the trigger matching in the HPTDC is its capability to assign hit measurements to multiple triggers.

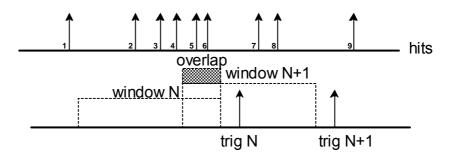

Fig. 2.5: Trigger matching windows overlap

If the Fig 2.5 shows hits received by one TDC, the events have the fallowing structure:

TDC header, event id N, trigger time tag N (if enabled)

DATUM Hit time 2

DATUM Hit time 3

DATUM Hit time 4

DATUM Hit time 5

DATUM Hit time 6

TDC trailer, event id N, number data 5 (if enabled)

TDC header, event id N+1, trigger time tag N+1 (if enabled)

DATUM Hit time 5

DATUM Hit time 6

DATUM Hit time 7

**DATUM Hit time 8**

TDC trailer, event id N+1, number data 4 (if enabled)

## 2.4.1. Timing constraints

The trigger matching related parameters must be programmed according to the following constraints.

1st case: the trigger matching window precedes the trigger arrival:

Fig. 2.6: Storage of hits occurred prior triggering

The window width and the window offset are encoded on 12 bit (25 ns LSB):

Match window width < |window offset|  $\le 4095$  clock cycle = 102375 ns

Note that in this case the window offset is negative.

2<sup>nd</sup> case: the trigger matching window is "straddling" the trigger or delayed with respect to the trigger:

Fig. 2.7: Storage of hits which may occur after triggering

As previously described, the HPTDC does not allow to program a trigger matching window straddling the trigger or delayed with respect to the trigger; anyway this is allowed in the V1190, by providing a 1 µs (40 clock cycles) delay on the trigger; the allowed trigger matching windows must thus agree with the following constraint:

Match window width + window offset  $\leq$  40 clock cycles = 1000 ns

Note that in this case the Window offset can be either negative or positive, see Fig. 2.7.

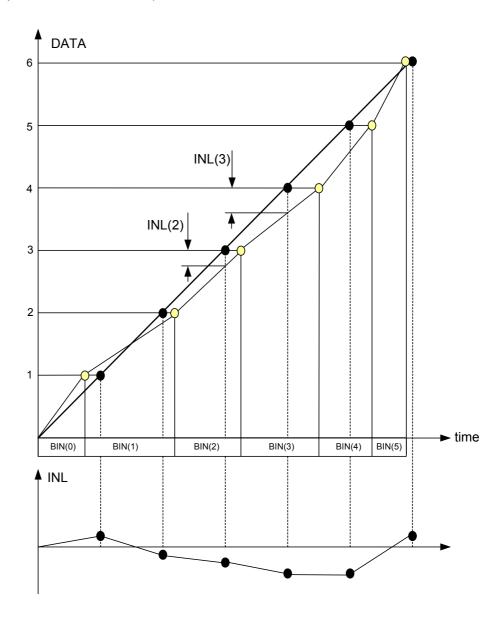

### 2.5. **Integral-non-linearity Compensation**

The INL represents the error of the Input-Output characteristic *t-D* of the TDC respect to the ideal one which is given by the following function:

D(t) = int (t / LSB)ideal characteristic

Where **D** is the output data, **t** is the input time, **LSB** is the bin size (800, 200 or 100ps) and int(x) represents the integer part of x.

NOTE: with analog circuit based TDCs, there is a variation of the LSB size due to the variation of gain and offset of the analog parts; in this case, the ideal input-output characteristic is given by the **best-fit line** calculated on the real input-output curve of the TDC (the best fit line is that one which minimizes the RMS error); the INL is then calculated as the difference between the curve and the best fit line. In the case of digital TDC (like the V1190), the gain and the offset come from a clock and it is very precise, so the ideal line can be calculated a priori without any interpolation (gain = 1/LSB, offset = 0). It must be noticed that the TDC chips feature an intrinsic INL, due to DNL, which has a 25 ns period ( = Tclock).

Fig. 2.8 INL I/O Characteristic

Fig. 2.9 INL trace @ 200ps

19

Title:

Mod. V1190-VX1190 A/B, 128/64 Ch Multihit TDC

Fig. 2.10 INL trace @ 100ps

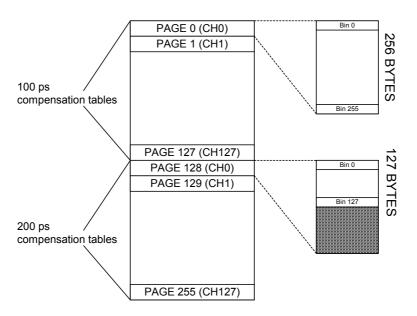

The INL curve can be corrected using a compensation look-up table: the curve is periodic so the LUT will cover only the BINs in a clock period (i.e. 256 entries when LSB=100 ps). A sample which falls in a certain BIN inside the clock period is corrected by the subtraction of the INL value for that BIN.

The INL compensation has been done only for 200 ps and 100 ps resolutions. For 800 ps the INL is good and there isn't any advantage in compensating it.

LSB = 200 ps:

LUT[n] = round(INL[n])n=[0:127]

D' = D - LUT[D & 0x7F]

LSB = 100 ps:

LUT[n] = round(INL[n]) n=[0:255]

D' = D - LUT[D & 0xFF]

NOTE: after the compensation, some missing codes can appear on the histogram; in fact, all the BINs are "scrambled" by the LUT and it is possible that BIN[x] is moved into BIN[y] but no BIN[z] is moved into BIN[x] which remains empty.

Fig. 2.11 RMS example @ 100ps (T4=85ns) after INL compensation

Fig. 2.12 INL for 100 ps after INL compensation

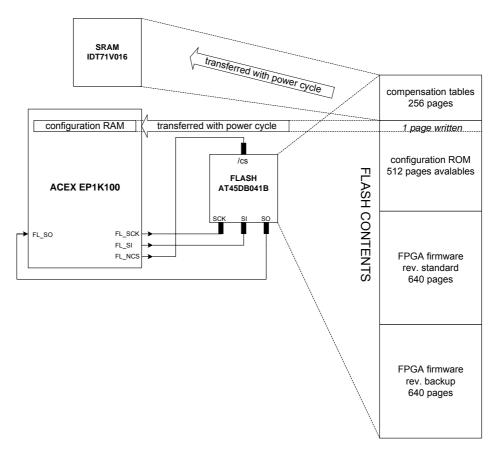

The Lock-Up table was calculated and loaded into the Flash Memory (see Appendix A). The INL compensation can be disabled by setting to 0 the compensation enable bit (bit 5) in the Control Register (default setting: compensation enabled, see § 6.3).

# 3. Technical specifications

### 3.1. **Packaging**

The modules are housed in a 6U-high, 1U-wide VME unit. The boards host the VME P1, and P2 connectors and fit into both VME standard and V430 backplanes.

### 3.2. **Power requirements**

The power requirements of the modules' versions are as follows:

Table 3.1: Model V1190 A/B power requirements

| Power supply | Mod. V1190 A | Mod. V1190 B |

|--------------|--------------|--------------|

| +5 V         | 5.50 A       | 2.90 A       |

### 3.3. **Front Panel**

Fig. 3.1: Model V1190 A/V1190 B front panels

Fig. 3.2: INPUT connector pin assignment

Fig. 3.3: INPUT connector cabling (Mod. A967 Cable Adapter)

### 3.4. **External connectors**

The location of the connectors is shown in Fig. 3.1. Their function and electro-mechanical specifications are listed in the following subsections.

#### 3.4.1. INPUT connectors

Mechanical specifications (Mod. V1190 A):

N. 4 High Density connectors<sup>4</sup>, Robinson Nugent P50E-068-P1-SR1-TG type, (34+34) pins; for the 128 single channel inputs.

Connector A refers to Channels 0 to 31.

Connector B refers to Channels 32 to 63.

Connector C refers to Channels 64 to 95.

Connector D refers to Channels 96 to 127.

Electrical specifications:

ECL/LVDS input signals, 110  $\Omega$  impedance. The 17th higher pair of pins of each connector's side is not connected.

25

<sup>&</sup>lt;sup>4</sup> The CAEN Mod. A967 cable adapter, which allows to adapt one High Density connector into two 1" 17+17pin Header-type connectors, is available. Mod. V1190 B has Connector 0÷31 and 32÷63 (64 ch).

#### 3.4.2. CONTROL connector

Mechanical specifications:

two 8+8-pin, 3M 3408-5202 Header-type connectors.

- AUX: not used.

- OUT\_PROG: differential ECL level, 110  $\Omega$  impedance.

- L2\_REJECT: not used.

- L2 ACCEPT: not used.

- CLOCK: Rising-edge active, differential ECL level, 110  $\Omega$ ; 40 MHz max freq.

- CLR: Active high, differential ECL level, 110  $\Omega$  impedance; min. width 25 ns.

- TRIGGER: Rising-edge active, differential ECL level, 110 Ω; min. width 25 ns, double Trigger resolution: 75 ns.

- CRST: Rising-edge active, differential ECL level, 110  $\Omega$ ; min. width 25 ns.

Pin assignment is shown in Fig. 3.4.

Fig. 3.4: CONTROL connector pin assignment

#### 3.4.3. **EXTERNAL TRIGGER connectors**

Mechanical specifications:

two 00-type LEMO connectors (bridged).

Electrical specifications:

Rising-edge active, NIM, high impedance; min. width 25 ns, double Trigger resolution: 75 ns

If this input is used, a 50 Ohm termination is required; in daisy chain configuration, the termination must be inserted on the last board in the chain.

This signal is internally or-wired with the TRG signal on the Control Connector (see § 3.4.2)

# 3.5. Other front panel components

## 3.5.1. Displays

The front panel (refer to Fig. 3.1) hosts the following LEDs:

**DTACK:** Colour: green.

Function: it lights up green whenever a VME read/write

access to the board is performed.

**PWR:** Colour: green/red.

Function: it lights up green when the board is inserted into the crate and the crate is powered up; when it is red, it indicates that there is an over-current status: in this case, remove the overload source, switch the module off and then switch it on

again.

TERM: Colour: green.

Function: it lights up green when the lines of the control bus

are terminated.

**FULL:** Colour: red.

Function: it lights up when the Output Buffer is full.

**ERROR:** Colour: red.

Function: it lights up to signal a TDC global error

**DRDY:** Colour: yellow.

Function: it lights up when at least one event/data (depending on acquisition mode, see § 6.4) is present in the Output

Buffer.

N.B.: FULL, ERROR and DRDY LEDs light up for a while at power ON to indicate that the board is configuring.

# 3.6. Internal hardware components

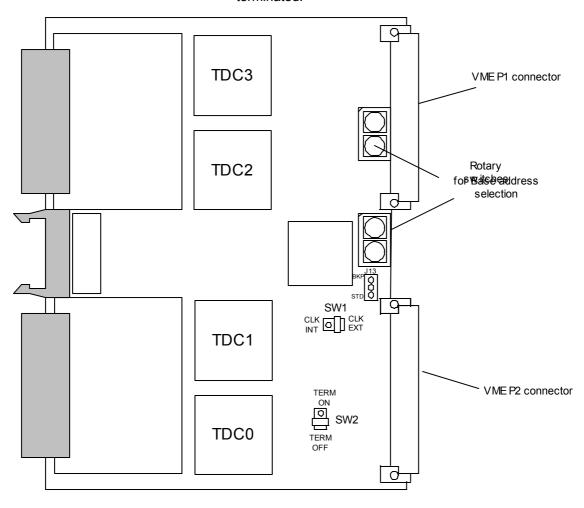

The V1190 A module is constituted by a motherboard with 2 piggy-back boards plugged into it. The V1190 B has no piggy-back board. In the following some hardware setting components, located on the boards, are listed. See Fig. 3.5 for their exact location on the PCB and their settings.

### 3.6.1. Switches

**ROTARY SWITCHES:** *Type:* 4 rotary switches.

Function: they allow to select the VME address of the

module. See Fig. 3.5 for their location.

**SW1:** *Type:* DIP switch.

**SW2**:

Function: it allows to switch from/to internal/external clock

Right position (dot visible): external clock;

Left position (dot not visible): internal clock.

Type: DIP switch.

*Function:* it allows the hardware termination (if enabled) of the Control Bus on 110  $\Omega$  (see also § 6.3)

**Low position** (dot visible): Control Bus not terminated;

**High position** (dot not visible): Control Bus terminated.

Fig. 3.5: Component Location (V1190 A<sup>5</sup>)

-

<sup>&</sup>lt;sup>5</sup> Mod. V1190 B has two TDC chips only

# 3.7. Technical specifications table

Title:

Table 3.2: Model V1190 A/B technical specifications

| Packaging                                 | 6U-high, 1U-wide VME unit                                                          |  |

|-------------------------------------------|------------------------------------------------------------------------------------|--|

| Power requirements                        | Refer to Table 3.1                                                                 |  |

| Inputs                                    | V1190 A/B: 128/64 ECL and LVDS inputs, 110 Ω impedance                             |  |

| Double hit resolution                     | 5 ns                                                                               |  |

| Acquisition modes                         | Trigger Matching Mode; Continuous Storage Mode                                     |  |

| Match window                              | Programmable (see § 5.3)                                                           |  |

| Built-in memory                           | 32 kwords deep Output Buffer                                                       |  |

| LSB                                       | VME programmable: 100 / 200 / 800 ps                                               |  |

| Dynamic Range                             | 104 μs (200 ps and 800 ps LSB); 52 μs (100 ps LSB)                                 |  |

| Dynamic Kange                             | <320 ps @ 800 ps res.                                                              |  |

| RMS resolution                            | <140 ps @ 200 ps res.                                                              |  |

| (with compensation <sup>6</sup> enabled)  | <80 ps @ 100 ps res.                                                               |  |

|                                           | <0.3 LSB @ 800 ps res.                                                             |  |

| Integral non linearity                    | <0.5 LSB @ 300 ps res.                                                             |  |

| (with compensation <sup>6</sup> enabled)  | <1 LSB @ 100 ps res.                                                               |  |

|                                           | <0.2 LSB @ 800 ps res.                                                             |  |

| Max. differential non linearity           | <0.3 LSB @ 200 ps res.                                                             |  |

| (with compensation <sup>6</sup> disabled) | <0.5 LSB @ 100 ps res.                                                             |  |

| Interchannel Isolation                    | ≤0.7 LSB                                                                           |  |

| Offset spread                             | <2 ns <sup>7</sup>                                                                 |  |

| EXT TRIGGER input                         | Two LEMO 00 bridged connectors, NIM signal, 50 $\Omega$                            |  |

| Double Trigger resolution                 | 75 ns                                                                              |  |

| Clock source                              | Internal (40 MHz) or External (on <i>Control</i> connector), dip switch selectable |  |

|                                           | active-high, differential ECL input signals:                                       |  |

|                                           | CLR: performs the Hardware CLEAR (min. width: 25 ns), see § 4.8.1                  |  |

|                                           | rising-edge active, differential ECL input signals:                                |  |

|                                           | CRST: performs the Bunch RESET (min. width: 25 ns), see § 4.8.5                    |  |

| Control inputs                            | CLK: external clock (max. freq.: 40 MHz)                                           |  |

|                                           | TRG: trigger for the TDC latching (min. width: 25 ns)                              |  |

|                                           | L2_A;                                                                              |  |

|                                           | L2_REJ.                                                                            |  |

|                                           | differential ECL output signal:                                                    |  |

| Control outputs                           | OUT_PROG: control output signal, programmable via the                              |  |

|                                           | out prog control register (see § 6.23)                                             |  |

|                                           | DTACK: green LED; lights up at each VME access.                                    |  |

|                                           | PWR: green/red LED; green: power ON, red: failure status.                          |  |

| Displays                                  | TERM: green LED; control bus termination ON.                                       |  |

| Diopiayo                                  | FULL: red LED; memory full.                                                        |  |

|                                           | ERROR: red LED; TDC global error.                                                  |  |

|                                           | DRDY: yellow LED; at least one datum/event in the Output Buffer                    |  |

|                                           | Addressing modes: A24, A32, MCST                                                   |  |

| VME                                       | Data transfer modes: D16, D32, MBLT32, BLT64, CBLT32, CBLT64                       |  |

|                                           | Readout rate: 33 Mbyte/s                                                           |  |

<sup>&</sup>lt;sup>6</sup> See § 2.5

<sup>&</sup>lt;sup>7</sup> It can be compensated via Offset Adjust, see § 5.7

# 4. Operating modes

#### 4.1. Installation

The Mod. V1190 A/B boards fit into both V430 VME 6U (JAUX dataway) and standard 6U VME crates. The boards support live insertion/extraction into/from the crate, i.e. it is possible to insert or extract them from the crate without turning the crate off.

CAUTION: all cables connected to the front panel of the board must be removed before extracting/inserting the board from/into the crate.

ALL CABLES MUST BE REMOVED FROM THE FRONT PANEL BEFORE EXTRACTING THE BOARD FROM THE CRATE!

### 4.2. **Power ON sequence**

To power ON the board follow this procedure:

- 1. insert the V1190 A/B board into the crate: as the board is inserted, the PWR green LED (see § 3.5.1) lights up indicating that the board is powered;

- 2. after insertion, the TERM LED lights up green (if the TERM switch is ON), the FULL LED and the ERROR LED become red and the DRDY LED becomes yellow; this indicates that the board is turned on and is configuring;

- 3. after a few seconds, the FULL, the ERROR and the DRDY LEDs will light off: this indicates that the board is ready to acquire data.

N.B.: if the PWR LED becomes red instead of being green, there is an overload and the over-current protection is now running. In order to acquire data, it is necessary to remove the overload source, then turn the board off and switch it on again. Sometimes, it may happen that the PWR LED is red as soon as the board is inserted in the crate: this is due to the fact that the board has been just misplaced into the crate. In this case, extract the board and insert it again into the crate.

**Revision:**

### 4.3. **Power ON status**

Title:

At power ON the module is in the following status:

Mod. V1190-VX1190 A/B, 128/64 Ch Multihit TDC

- the Output Buffer is cleared;

- registers are set to their default configuration (see § 5 and § 6);

- the TDCs are in the following status (see also § 5):

| trigger matching             | disabled        |

|------------------------------|-----------------|

| matching window width        | 500 ns (0x14)   |

| matching window offset       | -1 μs (0xFFD8)  |

| extra search window          | 200 ns (0x8)    |

| reject margin                | 100 ns (0x4)    |

| keep token                   | set             |

| subtraction trigger time     | disabled        |

| global offset                | 0               |

| channel offset               | 0 (all channel) |

| edge detection               | leading         |

| trailing/leading resolution  | 100 ps          |

| width pair mode resolution   | 100 ps          |

| TDC header/Trailer           | enabled         |

| error mark                   | enabled         |

| error bypass                 | disabled        |

| error type                   | all enabled     |

| dead time between hits       | 5 ns            |

| TDC readout FIFO size        | 256             |

| max number of hits per event | no limit        |

| channels                     | all enabled     |

At power ON or after a hardware reset the module must thus be set to the desired configuration.

### **Addressing capability** 4.4.

The module can be addressed in 2 different ways, specifically:

- 1. via Base Address;

- 2. via Multicast/Chained Block Transfer addressing mode.

**Revision date:**

06/12/2005

### 4.4.1. Addressing via Base Address

Title:

The module works in A24/A32 mode. This implies that the module's address must be specified in a word of 24 or 32 bit. The Address Modifier codes recognised by the module are summarised in Table 4.1.

Table 4.1: Module recognised Address Modifier

| A.M. | Description                              |

|------|------------------------------------------|

| 0x3F | A24 supervisory block transfer           |

| 0x3E | A24 supervisory program access           |

| 0x3D | A24 supervisory data access              |

| 0x3C | A24 supervisory 64 bit block transfer    |

| 0x3B | A24 non privileged block transfer        |

| 0x3A | A24 non privileged program access        |

| 0x39 | A24 non privileged User data access      |

| 0x38 | A24 non privileged 64 bit block transfer |

| 0x0F | A32 supervisory block transfer           |

| 0x0E | A32 supervisory program access           |

| 0x0D | A32 supervisory data access              |

| 0x0C | A32 supervisory 64 bit block transfer)   |

| 0x0B | A32 non privileged block transfer        |

| 0x0A | A32 non privileged program access        |

| 0x09 | A32 non privileged data access           |

| 0x08 | A32 non privileged 64 bit block transfer |

The Base Address can be selected in the range:

0x000000  $\leftarrow \rightarrow$ 0xFF0000 A24 mode 0x00000000  $\leftarrow \rightarrow$ 0xFFFF0000 A32 mode

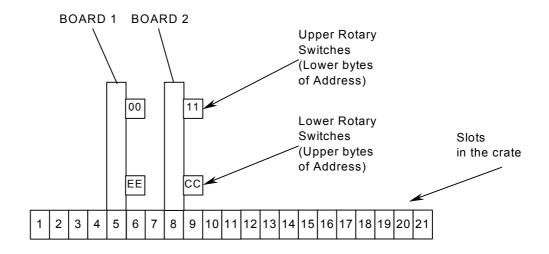

The Base Address of the module can be fixed through four rotary switches, housed on two piggy-back boards plugged into the main printed circuit board (see § 3.6.1)

### 4.4.2. Base addressing examples

The following is an example of Base Addressing for two boards inserted in a VME crate.

Fig. 4.1: Base Addressing: Example 1

If the board 1 and board 2 are respectively with the rotary switches for VME Base Addressing set as shown in the figure, the complete address of the registers of the two boards will be as follows:

## Board 1:

Base addressing A32: 0xEE000000 + offset Base addressing A24: 0x000000 + offset

Board 2:

Base addressing A32: 0xCC110000 + offset Base addressing A24: 0x110000 + offset

### 4.4.3. MCST/CBLT addressing

When the Multicast/Chained Block Transfer addressing mode is adopted, the module works in A32 mode only. The Address Modifiers codes recognised by the module are:

| MCST: | 0x0E | A32 supervisory block transfer           |

|-------|------|------------------------------------------|

|       | 0x0D | A32 supervisory 64 bit block transfer    |

|       | 0x0A | A32 non privileged block transfer        |

|       | 0x09 | A32 non privileged 64 bit block transfer |

| CBLT: | 0x0F | A32 supervisory block transfer           |

|       | 0x0C | A32 supervisory 64 bit block transfer    |

|       | 0x0B | A32 non privileged block transfer        |

|       | 0x08 | A32 non privileged 64 bit block transfer |

The boards can be accessed in Multicast Commands mode (MCST mode, see [2]), that allows to write in the registers of several boards at the same time by accessing the MCST Base Address in A32 only once.

The boards can be accessed in Chained Block Transfer mode (CBLT mode, see [2]) that allows to readout sequentially a certain number of contiguous boards in a VME crate. This access is allowed in BLT32 and BLT64 modes only to the MCST Base Address.

N.B.: The Base Address used for MCST and CBLT operations is the same, i.e. throughout this User's Manual the "MCST Base Address" identifies the same Address, used both for MCST commands (in Write only, for the allowed registers) and the CBLT Readout (in Read only, for the Output Buffer only).

The MCST Base Address must be set in a different way from the ordinary Base Address. Its most significant byte (i.e. bits 31 through 24 of base address) must be written in the MCST/CBLT Address Register (see § 6.11) and must be set in common to all boards belonging to the MCST/CBLT chain (i.e. all boards must have the same setting of the MCST/CBLT Base Address on bits 31 through 24). The default setting is 0xAA.

In CBLT/ MCST operations, the IACKIN/ IACKOUT daisy chain is used to pass a token from one board to the following one. The board which has received the token stores/sends the data from/to the master via MCST / CBLT access. No empty slots must thus be left between the boards or, in alternative, empty slots can be left only in case VME crates with automatic IACKIN/IACKOUT short-circuiting are used.

Once the addresses have been set, the first and last board in a chain must have, respectively, only the FIRST BOARD (F B) and only the LAST BOARD (L B) bit set to 1 in the MCST Control Register (see § 6.12). On the contrary, all intermediate boards must have both the FIRST\_BOARD and the LAST\_BOARD bits set to 1 (active, intermediate) or both the FIRST\_BOARD and the LAST\_BOARD bits set to 0 (inactive). By default these bits are set to 0 (the board is inactive).

| Board status | Board position in the chain | F_B bit | L_B bit |

|--------------|-----------------------------|---------|---------|

| inactive     | -                           | 0       | 0       |

| active       | last                        | 0       | 1       |

| active       | first                       | 1       | 0       |

| active       | intermediate                | 1       | 1       |

Please note that in a chain there must be one (and only one) first board (i.e. a board with F B bit set to 1 and the L B bit set to 0) and one (and only one) last board (i.e. a board with F B bit set to 0 and the L B bit set to 1).

The complete address in A32 mode is:

**MCST/CBLT Address** A [31:24] A [23:16] 00

A [15:0] offset

In MCST/CBLT operation it is possible to define more chains in the same crate, but each chain must have an address different from the other.

N.B.: In CBLT operation the data coming from different boards are tagged with the HEADER and with the TRAILER words containing the GEO address in the 5 MSB (see § 4.4.2). It is up to the User to write the GEO address in the GEO register before executing the CBLT operation, since the V1190 A/B are not enabled to pick the GEO address from the VME Bus. If the GEO address is not written in the relevant register before performing the CBLT operation, it will not be possible to identify the module which the data are coming from.

Title:

Mod. V1190-VX1190 A/B, 128/64 Ch Multihit TDC

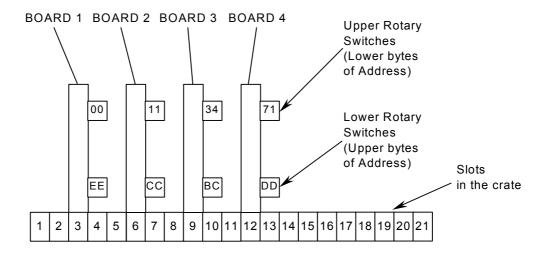

The following is an example of MCST and CBLT addressing for four V1190 A/B boards plugged into a VME crate. To access the boards the steps to be performed are as follows:

- 1. Set the MCST address (see § 6.11) for all boards via VME Base Address;

- 2. Set the bits F\_B and L\_B of the MCST Control Register (see § 6.12) according to the operational status (active or inactive) of each board and to its position in the chain (first, intermediate or last);

- 3. Write or read the boards via MCST/CBLT addressing.

An example of User procedures which can be used to perform a write access is:

vme\_write (address, data, addr\_mode, data\_mode)

which contain the following parameters:

Address: the complete address, i.e. Base Address + offset;

Data: the data to be either written;

Addr\_mode: the addressing mode (only A32 allowed in MCST);

Data\_mode: the data mode.

Fig. 4.2: MCST/CBLT Addressing Example

In the following, a software example, using the above mentioned procedures, is listed:

### Example of Access via Base Address

```

vme_write (0xEE001010, 0xAA, A32, D16)

/* set MCST Address=0xAA for board 1 */

vme write (0xCC111010, 0xAA, A32, D16)

/* set MCST Address=0xAA for board 2 */

vme write (0xBC341010, 0xAA, A32, D16)

/* set MCST Address=0xAA for board 3 */

/* set MCST Address=0xAA for board 4 */

vme write (0xDD711010, 0xAA, A32, D16)

vme write (0xEE001012, 0x02, A32, D16)

/* set board 1 = First */

vme write (0xCC111012, 0x03, A32, D16)

/* set board 2 = Active */

vme write (0xBC341012, 0x00, A32, D16)

/* set board 3 = Inactive */

vme_write (0xDD711012, 0x01, A32, D16)

/* set board 4 = Last */

```

**NPO:** 00104/03:V1X90.MUTx/06

**Filename:** V1190\_REV6.DOC

**Number of pages:** Page: 94 35

vme write (0xAA001014, 0x00, A32, D16) /\* send SOFTWARE RESET to all the boards \*/

N.B.: there must be always one (and only one) FIRST BOARD and one (and only one) LAST BOARD.

### 4.5. Interrupter capability

**Document type:**

User's Manual (MUT)

The Mod. V1190 A/B house a VME INTERRUPTER. The modules respond to D16 Interrupt Acknowledge cycles providing: a word whose 8 LSB are the STATUS/ID.

### 4.5.1. Interrupt Status/ID

The interrupt STATUS/ID is 8-bit wide, and it is contained in the 8 LSB of the Interrupt Vector Register (see § 6.9). The register is available at the VME address: Base Address + 0x100C.

#### 4.5.2. Interrupt Level

The module's interrupter produces its request on one of the 7 IRQ lines. The interrupt level is programmable via VME (see § 6.8).

### 4.5.3. Interrupt Generation

An Interrupt is generated when the number of words stored in the memory equals the value written in the Almost Full Level Register at the VME address: Base Address + 0x1022 (see § 6.19). If the value in Interrupt Level Register is set to 0 the interrupt is disabled (default setting).

### 4.5.4. Interrupt Request Release

The INTERRUPTER removes its Interrupt request when either a Read Access is performed to the Output Buffer so that the number of events stored in the memory decreases and becomes less than the value written in the Almost Full Level Register or when a module's clear is performed.

### 4.6. **Trigger Matching Mode data transfer**

The Output Buffer can be readout via VME through D32, BLT32, BLT64, CBLT32 and CBLT64 modes. The module has to be programmed in order to work in the required mode (see § 5.2.1), and some parameters have to be set in order to keep data aligned (i.e. to transfer an integer number of events per cycle). In the following each readout mode will be described in detail.

Nw is the number of words which compose an event (note that such number is not constant but changes from event to event). It's up to the user to verify the presence of valid data in the Output Buffer before read out; this can be performed via the Status Register read out (Data Ready Bit, see § 6.4). When a trigger signal occurs, an event is loaded into the Output Buffer (see § 6.2). The DATA\_READY bit in the Status Register is set to one when at least one event is present in the buffer.

### 4.6.1. D32 OUTPUT BUFFER readout (Trigger Matching)

This readout mode can be performed in two ways:

- Wait for DATA READY bit to be set, then readout the Nw words until the global Trailer (TRAILER).

- Start readout without waiting for DATA\_READY: if BERR is disabled, fillers will be readout until a global header is met (otherwise, if BERR is enabled, BERR is signalled and no filler is transferred); then Nw words will be transferred until a global TRAILER is readout.

### 4.6.2. BLT32/64 OUTPUT BUFFER readout with Bus Error and Event Aligned BLT disabled

BLT32/64 readout with BERR and Event Aligned BLT mode disabled does not permit to collect one or more complete events since the number of bytes Nb which are transferred in a BLT cycle has usually a "typical" value (256, 2048...) which rarely coincide with a multiple of the number of bytes **NB** composing an event, i.e. NB=Nw-4 (note that Nw is not constant but changes from event to event). It is more than likely that in a BLT cycle an event could be partially read out and the remaining part would be read out in the subsequent cycle. If the Output Buffer contains a number N of words smaller than Nb/4 (the number of words readout in one BLT cycle), the module transfers its memory content, completed with (Nb/4)-N fillers.

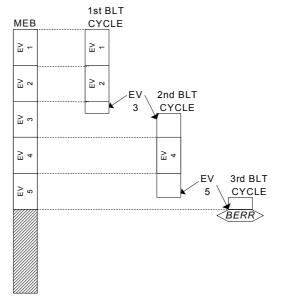

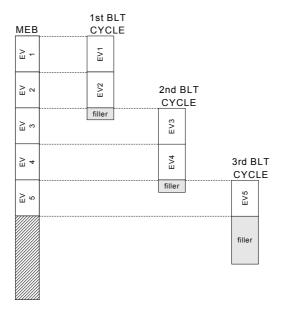

Fig. 4.3 Example of BLT data transfer with BERR and Event Aligned BLT disabled

#### 4.6.3. BLT32/64 OUTPUT BUFFER readout with Bus Error enabled

In this mode the module produces a BERR signal (see § 6.3) once the last data in the Output Buffer has been transferred and no filler is added.

Fig. 4.4 Example of BLT data cycle with BERR enabled and Event Aligned BLT disabled

# 4.6.4. BLT32/64 OUTPUT BUFFER readout with Event Aligned BLT enabled

This mode allows to transfer an integer number Ne of events (in fig. 4.5 Ne = 2), set via the BLT Event Number Register (see § 6.20). The default setting value of this register is 0, so this mode disabled. In order to enable the Event Aligned BLT the desired number of events Ne must be written in the BLT event number register. This mode allows the module to transfer a maximum number Ne of events; three cases may occur:

- The memory has a number of events smaller than Ne: the module transfers its memory content (with one or more BLT cycles) and completes the cycle adding fillers (see § 6.2.3).

- The memory has a number of events larger than Ne and Nb/4>  $\Sigma$ Nw  $^8$  (where Nb/4 is the number of words transferred in one BLT cycle): the module transfers Ne events per cycle and eventually completes the cycle adding fillers.

- The memory has a number of events larger than Ne and Nb/4< ΣNw: the transfer requires more than one cycle to be completed, the last cycle eventually is completed with fillers.

Fig. 4.5 Example of BLT data cycle with BERR disabled and Event Aligned BLT enabled

-

$<sup>^{8} \</sup>Sigma Nw = total number of words$

Title:

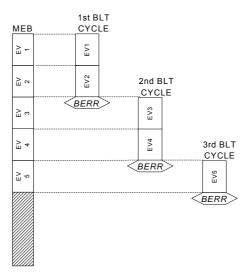

### 4.6.5. BLT32/64 OUTPUT BUFFER readout with both Event Aligned BLT and Bus Error enabled

This mode allows the module to transfer a maximum number Ne of events; three cases may occur:

- The memory has a number of events smaller than Ne: the module transfers its memory content (with one or more BLT cycles) then asserts BERR, thus terminating the cycle.

- The memory has a number of events larger than Ne and Nb/4>  $\Sigma$ Nw: the module transfers Ne events in one cycle, then asserts BERR thus terminating the cycle.

- The memory has a number of events larger than Ne and Nb/4<  $\Sigma$ Nw: the transfer requires more than one cycle to be completed.

N.B.: Enabling the BERR is useful in order to save time, avoiding fillers' transfer.

Fig. 4.6 Example of BLT data transfer with BERR and Event Aligned BLT enabled

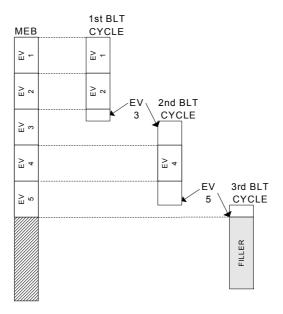

#### 4.6.6. CBLT32/64 OUTPUT BUFFER readout

The CBLT mode allows data readout from a set of modules in the crate. The readout starts from the first module of the set: it transfers its first event, then passes the token to the subsequent module via the IACKIN/IACKOUT daisy chain lines. If one module's Output Buffer is empty or *Inactive* (see § 6.12), the token is passed with no data transfer. If the data transfer is not completed by the first CBLT cycle, a second one may be attached to the first and so on until the last module in the set has transferred its last data: then it asserts BERR, which is automatically enabled when the CBLT is performed, thus completing the cycle.

CBLT64: if an odd number of words is transferred, the Board completes the event transfer by adding a filler.

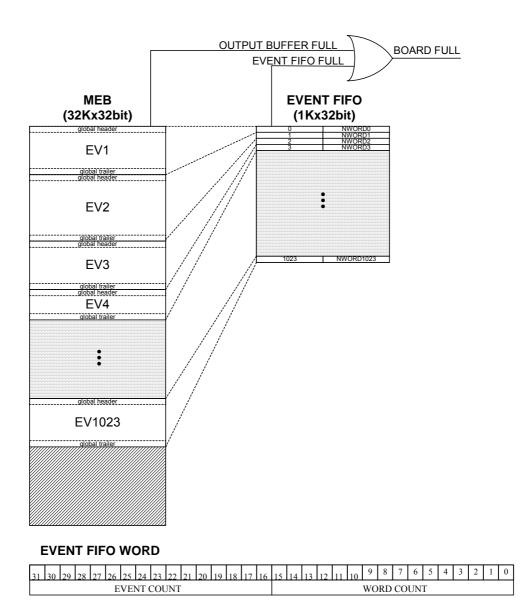

### 4.6.7. D32 and BLT32/MBLT readout with Event FIFO enabled

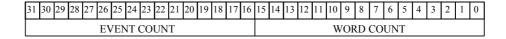

The Event FIFO has been introduced in order to help the event readout from the Output Buffer, since the events length is unknown a priori. If the Event FIFO is enabled when an event is written in the Output Buffer, the FPGA writes in its internal FIFO (1 kword) a 32 bit word containing the event counter on 16 bit and the event number of words (see § 6.18).

This allows to acknowledge the number of words that compose the event, before starting the event readout. If the Event FIFO is enabled the events are readout in the following way:

- Readout one (or N) word frome the Event FIFO

- Calculate Nw (or  $\Sigma$ Nw): number of words which compose the event (or N events)

- Readout Nw (or  $\Sigma$ Nw) in D32 /BLT32 / MBLT

Note that if the Event FIFO is enabled, for each event a 32 bit word is written into the Event FIFO: if it is never readout, then the board would become FULL after 1024 events, although the Output Buffer would be EMPTY (all the events were readout).

The Event FIFO Status Register and the Event FIFO Stored Register allow to know how many words are written into the Event FIFO (that, if it is correctly readout as described, correspond to the number of events stored into the Output Buffer).

Fig. 4.7 MEB readout with Event FIFO enabled

## 4.7. Countinuous Storage Mode data transfer

The Output Buffer can be readout via VME through either D32 or BLT32/BLT64 modes. The module has to be programmed in order to work in the required mode (see § 5.2.2). When hits are written into the Output Buffer; the DATA\_READY bit in the Status Register (see § 6.4) is set to one when at least one datum is present in the buffer.

### 4.7.1. D32 OUTPUT BUFFER readout (Continuous Storage)

This readout mode can be performed in two ways:

• Set the Almost Full Level to N (see § 6.19); wait until the Almost Full bit in the Status Register is set to one then readout the N recorded words in D32 mode.

- Readout continuously from the buffer, removing the "fillers" via software.

- If BERR is enabled and the Output Buffer is empty, then the board asserts BERR without filler transfer.

### 4.7.2. BLT32/64 OUTPUT BUFFER readout (Continuous Storage)

- If BERR is disabled and the Output Buffer contains a number N of words smaller than Nb/4 (the number of words readout in one BLT cycle, being Nb the number of bytes per cycle), the module transfers its memory content, completed with (Nb/4)-N fillers.

- If BERR is enabled the module produces a BERR signal once the last data in the Output Buffer has been transferred and no filler is added.

### 4.8. Reset logic

Different types of CLEAR or RESET operations are foreseen, according to the effects they have on the module and particularly on the registers. These are:

- Software CLEAR

- Hardware CLEAR

- Software RESET

- Hardware RESET

- Software EVENT COUNT RESET

- Hardware BUNCH COUNT RESET

#### 4.8.1. Software and Hardware CLEAR

The CLEAR (whether hardware or software) clears the data off the Output Buffer, the event counter and performs a TDCs global reset, which does not erase the TDCs programmation. A TDC global reset in fact clears all buffers in the TDCs, initialises all internal state machines and counters to their initial state and clears all detected error conditions.

The CLEAR can be forwarded in several ways:

- 1. Via software: Software Clear Register (see § 6.14)

- 2. When a write access to some Registers is performed (see table 4.2)

- 3. When a pulse is sent to the front panel CLR input.

- 4. When an OPCODE (see § 5) which foresees the TDC reprogrammation is executed

The module's registers whose content is erased by a CLEAR are listed in Table 4.2.

### 4.8.2. Software RESET

The Software Reset performs the same actions of the CLEAR, moreover it resets some other registers and initializes the TDCs to the default configuration. This type of RESET can be forwarded by performing a write access to the Single Shot Reset Register. All the registers reset by a Software RESET are marked in the column SR (Software Reset) in Table 4.2.

### 4.8.3. Hardware RESET

The Hardware RESET performs the same actions as the Software RESET and, moreover, it resets some other registers. All the registers reset by a Hardware RESET are marked in the column HR (Hardware Reset) in Table 4.2. This kind of RESET is performed:

- 1. at Power ON of the module;

- 2. via a VME RESET (SYS RES).

After a reset (HW or SW) the module must thus be initialised.

### 4.8.4. Software Event Count RESET

The Software Event Count RESET does not perform the board's event counter reset but it loads the programmed event count offset into the TDCs event id counter. The Event Counter is also reset by the hardware Clear.

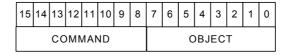

### 4.8.5. Hardware Bunch Count RESET